# **LECTURE NOTES**

**Analog Electronics & OP-AMP**

SEMESTER-6<sup>TH</sup>

**BISWAJIT MISHRA**

---- [DIODE & CIRCUITS] ---

# CONSTRUCTION & WORKING PRINCIPLE OF DIODE: -

When a p-type semiconductor is suitably joined to n-type semiconductor, the contact surface is called PN Junction. Most semiconductor devices contain one or more PN junctions.

### **4** Formation of PN junction.

- In actual practice, the characteristic properties of PN junction will not be apparent if a p-type block is just brought in contact with n-type block. In fact, it is **fabricated** by special techniques.

- > There are a number of techniques for the fabrication of PN-Junction: -

- Grown Junction

- Alloy Junction

- Diffused Junction

- Epitaxial Growth

- Point contract Junction.

- > But the most common method of making PN junction is called Alloying.

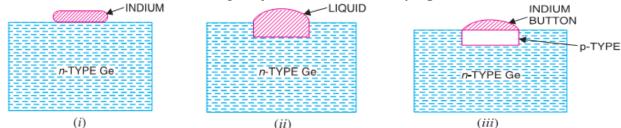

[Figures of different stages of formation of PN junction by Alloying method]

- In this method, a small block of indium (trivalent impurity) is placed on an n-type germanium slab as shown in Fig (i). The system is then heated to a temperature of about 500°C.

- The indium and some of the germanium melt to form a small puddle of molten germanium-indium mixture as shown in Fig (ii).

- The temperature is then lowered and puddle begins to solidify. Under proper conditions, the atoms of indium impurity will be suitably adjusted in the germanium slab to form a single crystal. Addition of indium overcomes the excess of electrons in the n-type germanium to such an extent that it creates a p-type region. As the process goes on, the remaining molten mixture becomes increasingly rich in indium.

- When all germanium has been redeposited, the remaining material appears as indium button which is frozen on to the outer surface of the crystallized portion as shown in Fig. (iii).

# **4** Properties of PN Junction.

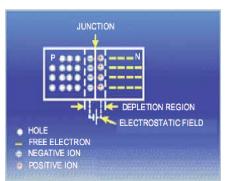

- To explain PN junction, consider two types of materials: 1) P-Type & 2) N-Type.

- P-type semiconductor having –ive acceptor ions and +ive charged holes. N-type semiconductor having +ive donor ions & –ive free electrons.

- P-type has high concentration of holes and N-type has high concentration of electrons.

- So there is a tendency for the free electron to diffuse over p-side and holes to n-side. This process is called **Diffusion**.

- When a free electron move across the junction from n-type to ptype, positive donor ions are removed by the force of electrons. Hence positive charge is built on the n-side of the junction.

- Similarly negative charge establish on p-side of the junction.

- When sufficient no of donor and accepter ions gathered at the junction, further diffusion prevented. Because +ive charge on n-side repel holes to cross from p-side to n-side, similarly –ive charge on p-side repel free electrons to cross from n-type to p-type.

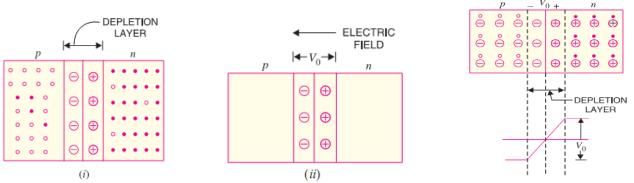

- > Thus a barrier is set up against further movement of charge carriers is hole or electrons. This barrier is called as **Potential Barrier**/Junction Barrier ( $V_0$ ) and is of the order 0.1 to 0.3 volt. This prevents the respective majority carriers for crossing the barrier region. This region is known as **Depletion Layer**

- [1.2]

- The term depletion is due to the fact that near the junction, the region is depleted (i.e. emptied) of charge carries (free electrons and holes) due to diffusion across the junction.

- It may be noted that depletion layer is formed very quickly and is very thin compared to the n-region and the p-region.

- Once pn junction is formed and depletion layer created, the diffusion of free electrons stops. In other words, the depletion region acts as a barrier to the further movement of free electrons across the junction. The positive and negative charges set up an electric field as shown in the fig above.

- The electric field is a barrier to the free electrons in the n-region. There exists a potential difference across the depletion layer and is called Barrier Potential (V<sub>0</sub>).

- The barrier potential of a pn junction depends upon several factors including the type of semiconductor material, the amount of doping and temperature.

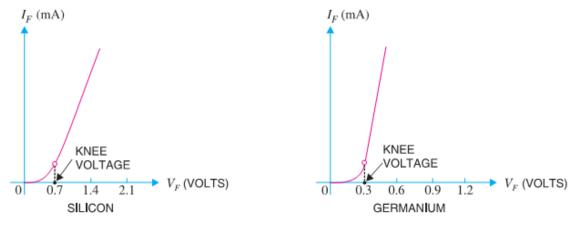

> The typical barrier potential is approximately: - For Silicon,  $V_0 = 0.7 \text{ V}$ ; For Germanium,  $V_0 = 0.3 \text{ V}$

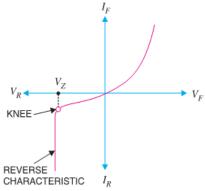

# \* Junction Capacitance:-

- When a PN junction is formed, a layer of positive and negative impurity ions is formed on either side of the pn junction. This depletion layer acts as dielectric (non-conductive) medium between P-region and N-region. Therefore, these regions act as two plates of a capacitor separated by dielectric medium.

- The capacitance formed in this junction is called as Depletion Layer Capacitance or Space Charge Capacitance or Transition Region Capacitance or simple Junction Capacitance.

# **4** Applying D.C. Voltage Across PN Junction or Biasing a PN Junction

- In electronics, the term bias refers to the use of D.C. voltage to establish certain operating conditions for an electronic device. In relation to a PN junction, there are following two bias conditions :

- 1. Forward Biasing 2. Reverse Biasing

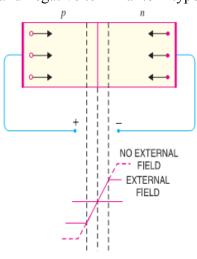

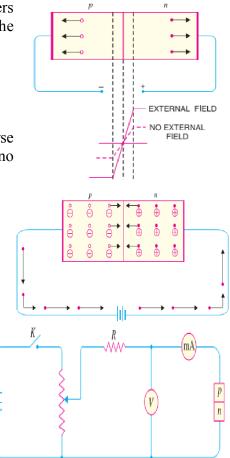

- Forward Biasing. When external D.C. voltage applied to the junction is in such a direction that it cancels the potential barrier, thus permitting current flow, it is called Forward Biasing.

- To apply forward bias, connect positive terminal of the battery to p-type and negative terminal to n-type as shown in Fig.

- The applied forward potential establishes an electric field which acts against the field due to potential barrier.

- > Therefore, the resultant field is weakened and the barrier height is reduced at the junction.

- ➤ As potential barrier voltage is very small (0.1 to 0.3 V), therefore, a small forward voltage is sufficient to completely eliminate the barrier.

- Once the potential barrier is eliminated by the forward voltage, junction resistance becomes almost zero and a low resistance path is established for the entire circuit.

- > Thus, current flows in the circuit. This is called **Forward Current**.

- ➤ With forward bias to PN junction, the important points are: -

- (i) The potential barrier is reduced and at some forward voltage i. e. (0.1 to 0.3 V), it is eliminated altogether.

- (ii) The junction offers low resistance (forward resistance,  $R_{\rm f})$  to current flow.

- (iii) Current flows in the circuit due to the establishment of low resistance path.

- (iv) The magnitude of current depends upon the applied forward voltage.

[1.3]

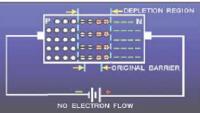

- Reverse Biasing. When the external D.C. voltage applied to the junction is in such a direction that potential barrier is increased, it is called Reverse Biasing.

- ➢ For reverse bias, connect -ve terminal of battery to p-type and +ve terminal to n-type as shown in Fig.

- ➢ It is clear that applied reverse voltage establishes an electric field which acts in the same direction as the field due to potential barrier.

- Therefore, the resultant field at the junction is strengthened and the barrier height is increased as shown in Fig.

- The increased potential barrier prevents the flow of charge carriers across the junction. Thus, a high resistance path is established for the entire circuit and hence the current does not flow.

- With reverse bias to PN junction, The important points are:

- (i) The potential barrier is increased.

- (ii) The junction offers very high resistance  $R_r$ ) to current flow.

- (iii) No current flows in the circuit due to high resistance path.

- Conclusion: From the above discussion, it follows that with reverse bias to the junction, a high resistance path is established and hence no current flow occurs.

- Whereas with forward bias to junction low resistance path is set up & hence current flows in the circuit.

- Current Flow in a Forward Biased PN Junction:-

- It concluded that in n-type region, current carried by free electrons whereas in p-type region, it is carried by holes. However, in external connecting wires, current is carried only by free electrons.

# **4** Volt-Ampere Characteristics of PN Junction:-

- Volt-ampere or V-I characteristic of a pn junction (also called a crystal or semiconductor diode) is the curve between voltage across the junction and the circuit current.

- Usually, voltage is taken along x-axis and current along y-axis. Fig. shows the circuit arrangement for determining the V-I characteristics of a pn junction.

- The characteristics can be studied under three heads, namely: (1) Zero external voltage, (2) Forward Bias (3) Reverse Bias.

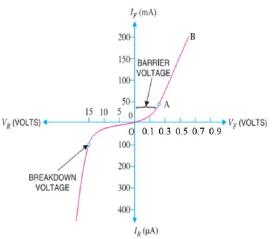

- (i) Zero external voltage: When the external voltage is zero, i.e. circuit is open at K; the potential barrier at the junction does not permit current flow. Therefore, the circuit current is zero as indicated by point O in Fig.

- (ii) Forward Bias: With forward bias to the pn junction i.e. p-type connected to positive terminal and n-type connected to negative terminal, the potential barrier is reduced. At some forward voltage (0.7 V for Si and 0.3 V for Ge), the potential barrier is altogether eliminated and current starts flowing in the circuit. From now onwards, the current increases with the increase in forward voltage.

- Thus, a rising curve OB is obtained with forward bias as in Fig. From the forward characteristic, it is seen that at first (region OA), the current increases very slowly and the curve is non-linear. Because the external applied voltage is used up in overcoming the potential barrier.

- > Once external voltage exceeds potential barrier voltage, the pn junction behaves like ordinary conductor.

- Therefore, the current rises very sharply with increase in external voltage (region AB on the curve). The curve is almost linear.

#### [1.4]

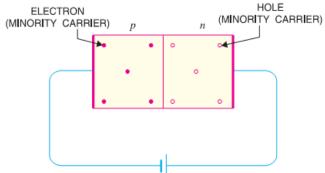

- (iii) Reverse Bias: With reverse bias to the pn junction i.e. p-type connected to negative terminal and n-type connected to positive terminal, potential barrier at the junction is increased. Therefore, the junction resistance becomes very high and practically no current flows through the circuit.

- > However, in practice, a very small current (of the order of  $\mu A$ ) flows in the circuit with reverse bias as

- shown in the reverse characteristic.

This is called **Reverse Saturation Current** (Is) and is due to the minority carriers.

- It may be recalled that there are a few free electrons in p-type material and a few holes in n-type material.

- These undesirable free electrons in p-type and holes in n-type are called minority carriers. As shown in side Fig. to these minority carriers, the applied reverse bias appears as forward bias.

- Therefore, a small current flows in the reverse direction. If reverse voltage is increased continuously, the kinetic energy of electrons (minority carriers) may become high enough to knock out electrons from the semiconductor atoms.

- ➤ At this stage breakdown of the junction occurs, characterized by a sudden rise of reverse current and a sudden fall of the resistance of barrier region. This may destroy the junction permanently.

- Note: -The forward current through a pn junction is due to the majority carriers produced by the impurity. However, reverse current is due to the minority carriers produced due to breaking of some co-valent bonds at room temperature.

### \* Important Terms: -

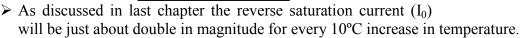

(i) Breakdown Voltage: - It is the minimum reverse voltage at which pn junction breaks down with sudden rise in reverse current.

(ii) Knee Voltage: - The forward voltage at which the current through the junction starts to increase rapidly. (iii) Peak inverse voltage (PIV):- It is the maximum reverse voltage that can be applied to the pn junction without damage to the junction. If the reverse voltage across the junction exceeds its PIV, the junction may be destroyed due to excessive heat. The peak inverse voltage is of particular importance in rectifier service.

(iv) Maximum forward current: - It is the highest instantaneous forward current that a pn junction can conduct without damage to the junction. Manufacturer's data sheet usually specifies this rating. If the forward current in a pn junction is more than this rating, the junction will be destroyed due to overheating.

(v) Maximum power rating: - It is the maximum power that can be dissipated at the junction without damaging it. The power dissipated at the junction is equal to the product of junction current and the voltage across the junction

### **4** Other Type of DIODES: -

| 1.                                 | Zener Diode    | 2.  | Light Emitting Diode | 3.  | Tunnel Diode     | 4.  | PIN Diodes              |

|------------------------------------|----------------|-----|----------------------|-----|------------------|-----|-------------------------|

| 5.                                 | Photo-Diode    | 6.  | Varactor Diodes      | 7.  | Laser Diodes     | 8.  | Gunn Diodes             |

| 9.                                 | Peltier diodes | 10. | Step Recovery Diodes | 11. | Schottky Diode   | 12. | Super Barrier Diodes    |

| 13.                                | Optoisolator   | 14. | Point-contact diodes | 15. | Avalanche diodes | 16. | Constant current diodes |

| <b>4</b> DIODE CURRENT EQUATION: - |                |     |                      |     |                  |     |                         |

- > The Mathematical equation, which describes the forward and reverse characteristics of a semiconductor diode is called the diode current equation.

- ► Let

- $I_0 =$  Reverse Saturation Current

I = Forward or Reverse Diode Current,

- V = External Voltage. (It is +Ve for Forward Bias, -Ve or Reverse Bias)

- $\eta$  = A constant, whose value is equal to 1 for Ge diode and 2 for Si diode for relatively low value of diode current (i.e. at or below the knee of the curve) and  $\dot{\eta}$  = 1 for Ge & Si diode for higher levels of diode current. (i. e. in the rapidly increasing section of the curve)

- $V_T$ =Volt-equivalent of temperature. Its value is given by the relation T/11,600,

- where T is the absolute temperature. At room temperature (i.e. 300K),  $V_T = 26vmV$ .

- $\succ$  The current equation for a forward biased diode is given by the relation,

$$I = I_0 \left( e^{V/\eta \cdot V} - 1 \right)$$

We know that at room temperature,  $V_T = 26mV = 0.026V$ . Substituting the value of  $V_T$  in the above equation it becomes,

$$I = I_0 (e^{40V/\eta} - 1)$$

> Thus diode current at or below the knee of the curve for Germanium and Silicon is given by

$$I_{Ge} = I_0 (e^{40V} - 1)$$

[As  $\eta = 1$  for Ge]

$I_{Si} = I_0 (e^{20V} - 1)$  [As  $\eta = 1$  for Si]

[1.5]

If the value of applied voltage is greater than unity (i.e. for the diode current in the rapid by increasing section of the curve) then the equation of diode current for Germanium or Silicon is given by

$$I = I_0 (e^{40V} - 1)$$

[As  $\eta = 1$  for Higher Value of Voltage]

The current equation for a reverse biased diode may be obtained by changing the sign of the applied voltage (V), i.e.

$$I = I_0 \left( e^{-V/\eta \cdot V} T - 1 \right)$$

- > If the Value of V>>V<sub>T</sub>, then the term  $-V/\eta$ .  $V_T << 1$ . Therefore  $I = I_0$ .

- > Thus the diode current under reverse bias is equal to the reverse saturation current as long as the external voltage is below its break down value.

### **↓** DIODE SPECIFICATION SHEET: -

- All manufactures of the semiconductor device provide data on specific diodes for the users to make proper utilization of the devices. This data could be a brief description limited to a one page or more than that. It includes the information arranged in table, graphs etc. The data is usually for : -

- Forward voltage, V<sub>F</sub> (At a specific Current & Temperature )

- Maximum forward current, I<sub>F</sub> (At a specific Temperature )

- Reverse saturation current  $I_R$  or  $I_O$  (At a specific Voltage & Temperature )

- Reverse Voltage Rating [PIV, PRV, VRRM or V(BR)], Where, BR=Breakdown at a specific current & temperature.

- Maximum power dissipation level at a particular temperature.

- Capacitance Value.

- Reverse recovery time, t<sub>rr</sub>.

- Operating temperature range.

- Beside this, depending on the type of diode being considered, more data may also be provided such as frequency range, noise level, switching time, thermal resistance level and peak repetitive values.

- ➤ For the application in mind, the significance of the data will usually be self apparent.

- > If the maximum power or dissipation rating is also provided, it is understood to be equal to the produce

$$D_{\text{Dmax}} = V_D I_D$$

Where  $I_D$  and  $V_D$  are the diode current and voltage at a particular point of operation.

# **DIODE APPLICATIONS:**

- A PN junction diode has an important characteristic that it conducts well in forward direction and poorly in reverse direction. This characteristic makes a diode very useful in a number of applications given below:

- 1. As Rectifiers or Power Diodes in D.C. power supply.

- 2. As Signal Diodes in communication circuits.

- 3. As Zener Diodes in voltage stabilizing circuits.

- 4. As Varactor Diodes in radio and TV receivers.

- 5. As a Switch in logic circuits used in computers

### **4** EFFECT OF TEMPERATURE OF DEPENDENCE OF JUNCTION DIODE:

- → We have already discussed in the last article that the diode current is a function of temperature and the temperature appears in the denominator of the exponent term of the diode current equation  $(i.e., V/\eta . V_T \text{ is equal to T/11600}).$

- It is thus obvious that with the increase in temperature, the exponent will reduce and hence the diode current should also decrease.

- > However, it has been found that the variation of saturation current  $(I_0)$  is much greater than the exponential term.

- The above fact may be expressed in the form of a mathematical relation as given below:

- Let,  $I_{01}$  = Saturation current at temp (T<sub>1</sub>) for Ge or Si diode,

- &  $I_{02}$  = Saturation current at some other temperature (T<sub>2</sub>)

$$I_{02} = I_{01} \cdot 2^{(T2 - T1)} / 10$$

- For example, a germanium diode with an I<sub>0</sub> in the order of 1 or 2μ A at 25°C has a leakage current of 100μ A (= 0.1 mA) at a temperature of 100°C.

- Current levels of this magnitude in the reverse bias region would certainly question our desired opencircuit condition in the reverse bias region.

- However, typical values of I<sub>0</sub> for silicon diode are much lower than that of germanium for similar power and current levels.

- > The increasing level of  $I_0$  with temperature account for the lower threshold voltage as shown in Fig.

- $\triangleright$  Due to this reason forward characteristic at 75°C is shown to the left to that of the characteristic at 25°C.

- As the temperature increases, the forward characteristic shifts more and more to the left of the characteristic at 25°C (i.e. become more and more "ideal").

- However, temperature beyond the normal operating range can have a very detrimental effect on the diode's maximum power and current levels.

- We see in Fig., that in the reverse bias region, the breakdown voltage is increasing with the increase in temperature.

IF

### 🚽 ZENER BREAK DOWN

Then

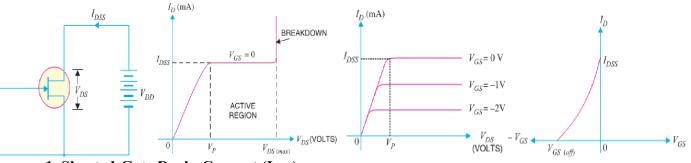

- It has already been discussed that when the reverse bias on a crystal diode is increased, a critical voltage, called Breakdown Voltage is reached where the reverse current increases sharply to a high value.

- The breakdown region is the knee of the reverse characteristic as shown in Fig. The satisfactory explanation of this breakdown of the junction was first given by the American scientist C. Zener.

- The breakdown voltage is also called Zener Voltage or Zener Break

Down & the sudden increase in current is known as Zener Current.

- The breakdown or Zener voltage depends upon the amount of doping.

- If the diode is heavily doped, depletion layer will be thin and consequently the breakdown of junction will occur at lower reverse voltage where as lightly doped diode has a higher breakdown voltage.

- **4** AVALANCHE BREAKDOWN: -

Forward Current

Reverse Current

Forward Voltage

Reverse Voltage

[1.7]

is

- In this case the increased reverse voltage increases the amount of energy imparted to minority carriers.

- As the reverse voltage is increased further the minority carriers acquires a large amount of energy.

- When these carriers collide with Si or Ge atoms, within the crystal structure, they impart sufficient energy to break a covalent bond and generate additional carriers (electron-hole pair).

- These additional carriers pick up energy from the applied voltage and generates still more carriers. As a result of this, the reverse current increases rapidly.

- This cumulative process of carrier generation (multiplication) is known as Avalanche Break down or Avalanche Multiplication

# **VARACTOR DIODE**

- A junction diode which acts as a variable capacitor under changing reverse bias known as a varactor diode. It is also known as Varicap or Voltcap.

- > When a pn junction is formed, depletion layer is created in the junction area.

- Since there are no charge carriers within the depletion zone, the zone acts as an insulator.

- The p-type material with holes (+ive charge) as majority carriers and n-type material with electrons (-ive charge) as majority carriers act as charged plates.

- Thus the diode may be considered as a capacitor with n-region and p-region forming oppositely charged plates and with depletion zone between them acting as a dielectric.

- > A varactor diode is specially constructed to have high capacitance under reverse bias.

- > The values of capacitance of varactor diodes are in the pico farad  $(10^{-12} \text{ F})$  range.

- > In normal operation, a varactor diode is always reverse biased.

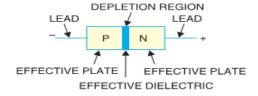

- > The capacitance of varactor diode is found as:

$$C_T = \varepsilon A/W_d$$

Where,

$C_T$  = Total capacitance of the junction,

A = Cross-sectional area of the junction,

$\epsilon$  = Permittivity of the semiconductor material,

- Wd = Width of the depletion layer.

- > When reverse voltage across a varactor diode is increased, the width Wd of the depletion layer increases. Therefore, the total junction capacitance  $C_T$  of the junction decreases.

- On the other hand, if the reverse voltage across the diode is lowered, the width Wd of the depletion layer decreases. Consequently, the total junction capacitance C<sub>T</sub> increases.

> It is used as Voltage Variable Capacitor, Voltage-Controlled Tuning

#

# INTRODUCTION: -

- Solution For reasons associated with economics of generation and transmission, the electric power available is usually an A.C. Supply. The supply voltage varies sinusoidal and has a frequency of 50 Hz. It is used for lighting, heating and electric motors.

- But there are many applications (e.g. electronic circuits) where D.C. supply is needed. When such a D.C. Supply is required, the mains A.C. Supply is rectified by using *Crystal Diodes*.

- ➤ The following two rectifier circuits can be used: -

- (i) Half-wave rectifier (ii) Full-wave rectifier

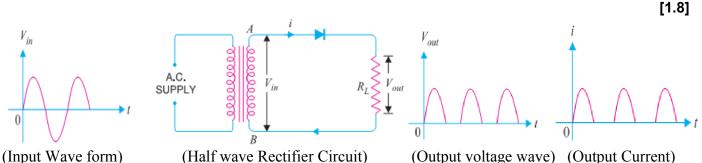

# SHALF-WAVE RECTIFIER:-

- In half-wave rectification, the rectifier conducts current only during the positive half-cycles of input A.C. Supply.

- The negative half-cycles of A.C. Supply is suppressed i.e. during negative half-cycles, no current is conducted and hence no voltage appears across the load.

# Great Circuit Details: -

- ➤ The above Fig shows the circuit where a single crystal diode acts as a half-wave rectifier.

- The A.C. Supply to be rectified is applied in series with the diode and load resistance  $R_L$ . Generally, A.C. Supply is given through a transformer.

- The use of transformer permits two advantages.

- $\checkmark$  Firstly, it allows us to step up or step down the A.C. input voltage as the situation demands.

- ✓ Secondly, the transformer isolates the rectifier circuit from power line and thus reduces the risk of electric shock.

### **4** OPERATION:-

- The A.C. voltage across the secondary winding AB changes polarities after every half-cycle.

- During the positive half-cycle of input A.C. voltage, end A becomes positive w.r.t. end B. This makes the diode forward biased and hence it conducts current.

- During the negative half-cycle, end A is negative w.r.t. end B. Under this condition, the diode is reverse biased and it conducts no current.

- Therefore, current flows through the diode during positive half-cycles of input A.C. voltage only; it is blocked during the negative half-cycles. In this way, current flows through load  $R_L$  always in the same direction. Hence D.C. output is obtained across  $R_L$ .

- $\gtrsim$  It may be noted that output across the load is *pulsating D.C.* These pulsations in the output are further smoothened with the help of filter circuits discussed later.

### **J**isadvantages : -

(i) The pulsating current in the load contains alternating component whose basic frequency is equal to the supply frequency. Therefore, an elaborate filtering is required to produce steady direct current.(ii) The A.C. supply delivers power only half the time. Therefore, the output is low.

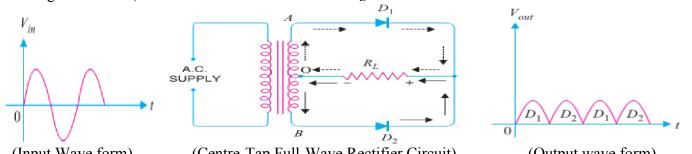

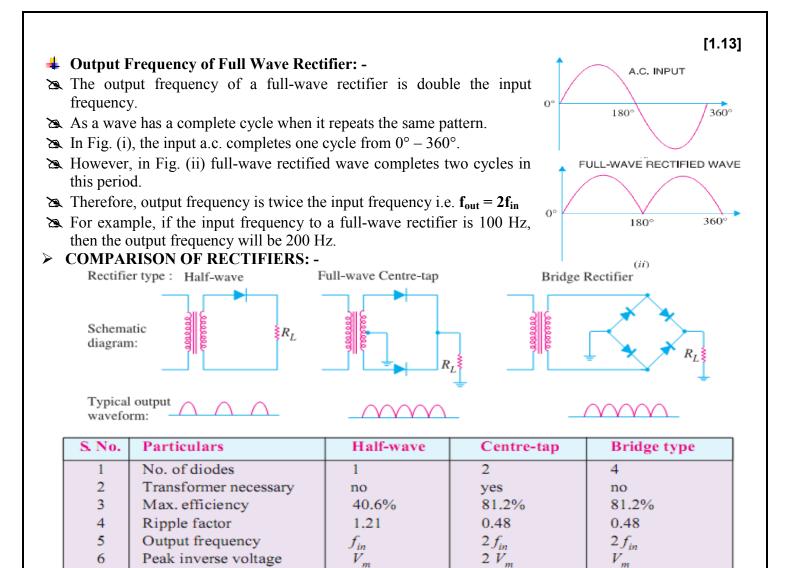

### ✤ FULL-WAVE RECTIFIER: -

- A In full-wave rectification, current flows through the load in the same direction for both half-cycles of input A.C. voltage. This can be achieved with two diodes working alternately.

- So For the positive half- cycle of input voltage, one diode supplies current to the load and for the negative half-cycle, the other diode does so ; current being always in the same direction through the load.

- Therefore, a full-wave rectifier utilizes both half-cycles of input A.C. voltage to produce the D.C. output.

- - (i) Centre-tap full-wave rectifier (ii) Full-wave bridge rectifier

### ✤ CENTRE-TAP FULL-WAVE RECTIFIER:-

### **4** Circuit Details: -

- The circuit employs two diodes  $D_1$  and  $D_2$  as shown in Fig below. A centre tapped secondary winding AB is used with two diodes connected so that each uses one half-cycle of input A.C. voltage.

- **A** In other words, diode  $D_1$  utilizes the A.C. voltage appearing across the upper half (OA) of secondary winding for rectification while diode  $D_2$  uses the lower half winding OB.

### Circuit Operation: -

- $\succeq$  During the positive half-cycle of secondary voltage, the end A of the secondary winding becomes positive and end B negative. This makes the diode D<sub>1</sub> forward biased and diode D<sub>2</sub> reverse biased.

- Therefore, diode  $D_1$  conducts while diode  $D_2$  does not. The conventional current flow is through diode  $D_1$ , load resistor  $R_L$  and the upper half of secondary winding as shown by the dotted arrows.

- $\mathbf{x}$  Therefore, diode  $D_2$  conducts while diode  $D_1$  does not. The conventional current flow is through diode D<sub>2</sub>, load R<sub>L</sub> & lower half winding shown by solid arrows.

- $\gtrsim$  It may be seen that current in the load R<sub>L</sub> is in the same direction for both half-cycles of input A.C. voltage. Therefore, D.C. is obtained across the load R<sub>L</sub>.

# (Input Wave form)

(Centre-Tap Full-Wave Rectifier Circuit)

(Output wave form)

### **Advantages:**-

- (i) The D.C. output voltage and load current values are twice than that of a half wave rectifier.

- (ii) The ripple factor is much less (0.482) than that of half rectifier (1.21).

- (iii) The efficiency is twice (81.2%) than that of half wave rectifier (40.6%).

### **Jisadvantages:-**

- (i) It is difficult to locate the centre tap on the secondary winding.

- (ii) The D.C. output is small as each diode utilizes only one-half of the transformer secondary voltage.

- (iii) The diodes used must have high peak inverse voltage.

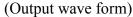

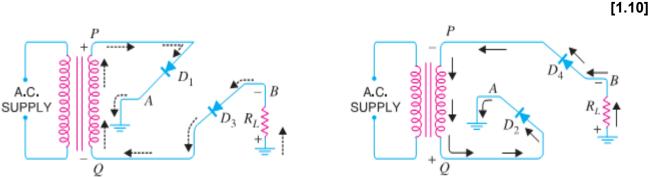

# FULL-WAVE BRIDGE RECTIFIER: -

# **4** Circuit Details: -

- The need for a centre tapped power transformer is eliminated in the bridge rectifier.

- **\succeq** It contains four diodes D<sub>1</sub>, D<sub>2</sub>, D<sub>3</sub> and D<sub>4</sub> connected to form bridge as shown in Fig below.

- The A.C. supply to be rectified is applied to the diagonally opposite ends of the bridge through the transformer.

- $\mathbf{x}$  Between other two ends of the bridge, the load resistance R<sub>L</sub> is connected.

(Input Wave Form) (Full-Wave Bridge Rectifier Circuit)

**GIRCUIT OPERATION :-**

- > During the positive half-cycle of secondary voltage, the end P of the secondary winding becomes positive and end Q negative.

- This makes diodes  $D_1$  and  $D_3$  forward biased while diodes D2 and D4 are reverse biased.

- $\mathbf{X}$  Therefore, only diodes D<sub>1</sub> and D<sub>3</sub> conduct. These two diodes will be in series through the load R<sub>L</sub> as shown in Fig. below. The conventional current flow is shown by dotted arrows. It may be seen that current flows from A to B through the load R<sub>L</sub>.

- makes diodes  $D_2$  and  $D_4$  forward biased whereas diodes  $D_1$  and  $D_3$  are reverse biased.

- Therefore, only diodes  $D_2$  and  $D_4$  conduct. These two diodes will be in series through the load  $R_L$  as shown in Fig. below. The current flow is shown by the solid arrows.

- A It may be seen that again current flows from A to B through the load i.e. in the same direction as for the positive half-cycle. Hence, D.C. output is obtained across load R<sub>L</sub>.

(Full-Wave Bridge Rectifier Circuit in +ve Half Cycle) (Full-Wave Bridge Rectifier Circuit -ve Half Cycle)

- Advantages: -

- (i) The need for centre-tapped transformer is eliminated.

- (ii) The output is twice that of the centre-tap circuit for the same secondary voltage.

- (iii) The PIV is one-half that of the centre-tap circuit (for same D.C. output).

- Disadvantages: -

- (i) It requires four diodes. (ii) Internal resistances high.

# **4** Mathematical Derivation for Rectification Efficiency for HALF WAVE rectifier : -

The ratio of d.c. power output to the applied input a.c. power is known as rectifier efficiency i.e.,

Rectifier efficiency,

$$\eta = \frac{\text{d.c. power output}}{\text{Input a.c. power}}$$

- > Consider a half-wave rectifier shown in Fig.

- $rac{}{\simeq}$  Let  $v = V_m \sin \theta$  be the alternating voltage that appears across the secondary winding. Let  $r_f$  and  $R_L$  be the diode resistance and load resistance respectively.

- The diode conducts during positive half-cycles of a.c. supply while no current conduction takes place during negative half-cycles.

- **OUTPUT D.C. POWER :-**

- A The output current is pulsating direct current. Therefore, in order to find D.C. power, average current has to be found out.

Average Value =

$$\frac{\text{Area Under The Curve Over a cycle}}{Base} = \int_0^{\pi} \frac{i \, de}{2\pi}$$

$$I_{av} = I_{dc} = \frac{1}{2\pi} \int_{0}^{\pi} i \ d\Theta = \frac{1}{2\pi} \int_{0}^{\pi} \frac{V_{m \ sin\Theta}}{rf + R_{L}} d\Theta = \frac{V_{m}}{2\pi (rf + R_{L})} \int_{0}^{\pi} sin\Theta \ d\Theta = \frac{V_{m \ sin\Theta}}{rf + R_{L}} [-\cos\Theta]_{0}^{\pi}$$

$$= \frac{V_{m}}{2\pi (rf + R_{L})} \times [(-\cos\pi) - (-\cos0)] = \frac{V_{m}}{2\pi (rf + R_{L})} \times 2 = \frac{V_{m}}{(rf + R_{L})} \times \frac{1}{\pi} = \frac{I_{m}}{\pi} \quad [\because I_{m} = \frac{V_{m}}{(rf + R_{L})}]$$

$$D.C. \text{ Power, } \mathbf{P}_{dc} = I_{dc}^{2} \times R_{L} = (\frac{I_{m}^{2}}{\pi}) \times R_{L}$$

$= V_m \sin \theta$

0

### **\* INPUT A.C. POWER: -**

22

▷ The A.C. power input is given by :  $P_{ac} = I_{rms}^2$  (rf + R<sub>L</sub>) For a half-wave rectified wave,  $I_{rms} = I_m/2$

$$\mathbf{P}_{ac} = \left(\frac{I_m}{2}\right)^2 \times \left(\mathbf{rf} + \mathbf{R}_L\right)$$

$$\therefore \qquad \text{Rectifier efficiency} = \frac{\text{d.c.output power}}{\text{a.c.input power}} = \left(\frac{(l_{m_L/\pi})^2 \times R_L}{(l_{m_L/2})^2 (\text{rf} + R_L)}\right) = \frac{0.406 \text{ R}_L}{\text{rf} + R_L} = \frac{0.406 \text{ R}_L}{1 + \frac{\text{rf}}{\text{R}_L}}$$

The efficiency will be maximum if  $r_f$  is negligible as compared to  $R_L$ .

### Max. Rectifier Efficiency for HALF WAVE Rectifier = 40.6%

➤ It shows that in half-wave rectification, a maximum of 40.6% of a. c. power is converted into d. c. power.

**NOTE:**

$$I_{\rm rms} = \left[\frac{1}{2\pi} \int_0^{2\pi} i^2 \, d\Theta\right]^{\frac{1}{2}} = \left[\frac{1}{2\pi} \int_0^{\pi} I_m^2 \sin^2 \theta \, d\Theta + \frac{1}{2\pi} \int_{\pi}^{2\pi} 0 \, d\Theta\right]^{\frac{1}{2}} = \left[\frac{I_m^2}{2\pi} \int_0^{\pi} \frac{1 - \cos 2\theta}{2} \, d\Theta\right]^{\frac{1}{2}}$$

$$= \left[\frac{I_m^2}{4\pi} \left[\Theta - \frac{\sin 2\theta}{2}\right]_0^{\frac{\pi}{2}}\right]^{\frac{1}{2}} = \left[\frac{I_m^2}{4\pi} \left[\pi - 0 - \frac{\sin 2\pi}{2} + \sin 0\right]\right]^{\frac{1}{2}} = \left[\frac{I_m^2}{4\pi} \times \pi\right]^{\frac{1}{2}} = \left[\frac{I_m^2}{4\pi}\right]^{\frac{1}{2}} = \frac{1}{2} \rightarrow I_{\rm rms} = \frac{1}{2}$$

Similarly,  $V_{rms} = V_m/2$  for Half Wave and For Full Wave Rectifier  $I_{rms} = I_m/\sqrt{2}$  and  $V_{rms} = V_m/\sqrt{2}$

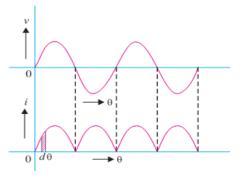

#### 🖊 Mathematical Derivation for Rectification Efficiency for FULL WAVE Rectifier : -

- **Fig.** shows the process of full-wave rectification.

- **Example 1** Let  $v = V_m \sin\theta$  be the a.c. voltage to be rectified. Let rf and  $R_L$  be the diode resistance and load resistance respectively.

- $\succeq$  Obviously, the rectifier will conduct current through the load in the same direction for both half-cycles of input a.c. voltage. The instantaneous current *i* is given by :

$$\mathbf{i} = \frac{v}{(\mathbf{rf} + \mathbf{R}_{\mathbf{L}})} = \frac{v_{\mathrm{m}} \sin\theta}{(\mathbf{rf} + \mathbf{R}_{\mathbf{L}})}$$

#### **\*** D.C. OUTPUT POWER.

The output current is pulsating direct current. Therefore, in order to find the d.c. power, average current has to be found out. For a full wave rectifier the average value or dc value can be found like half wave,

$$I_{dc} = \frac{2I_{m}}{\pi}$$

$$\therefore \text{ D.C. power output, } \mathbf{P}_{dc} = I_{dc}^2 \times \mathbf{R}_L = (\frac{2I_m}{\pi})^2 \times \mathbf{R}_L$$

### **\*** A.C. INPUT POWER.

The a.c. input power is given by :  $\Box$

$$P_{ac} = I_{rms}^2 (rf + R_L)$$

For a full-wave rectified wave, we have,  $I_{rms} = I_m / \sqrt{2}$

$$\mathbf{P}_{ac} = \left(\frac{I_m}{\sqrt{2}}\right)^2 (\mathbf{r}\mathbf{f} + \mathbf{R}_L)$$

: Full-wave rectification efficiency is

$$\eta = \frac{P_{dc}}{P_{ac}} = \frac{(2I_m/\pi)^2 R_L}{(\frac{I_m}{\sqrt{2}})^2 (rf + R_L)} = \frac{8}{\pi^2} \times \frac{R_L}{(rf + R_L)} = \frac{0.812 R_L}{rf + R_L} = \frac{0.812}{1 + \frac{rf}{R_L}}$$

The efficiency will be maximum if r<sub>f</sub> is negligible as compared to R<sub>L</sub>.

$\therefore$  Maximum efficiency = 81.2%

This is double the efficiency due to half-wave rectifier. Therefore, a full-wave rectifier is twice as effective as a half-wave rectifier.

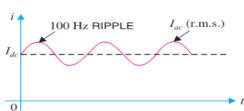

### **4 RIPPLE FACTOR: -**

- 🎘 The output of a rectifier consists of a d.c. component and an a.c. component (also known as ripple).

- The a.c. component is undesirable and accounts for the pulsations in the rectifier output.

- A The effectiveness of a rectifier depends upon the magnitude of a.c. component in the output; the smaller this component, the more effective is the rectifier.

- **A** Ripple mean unwanted ac signal present in the rectified output.

- The ratio of R.M.S. value of A.C. component to the D.C. component in the rectifier output is known as *ripple factor* i.e.

Ripple factor =

$$\frac{I.i.i.s. value of a.c. component}{value of d.c. component} = \frac{I_{ad}}{I_{dd}}$$

#### Mathematical Analysis.

- > The output current of a rectifier contains d.c. as well as a.c. component.

$$I_{\rm rms} = \sqrt{I_{do}^2 + I_{ao}^2}$$

Or  $I_{\rm ac} = \sqrt{I_{rms}^2 - I_{do}^2}$

$\mathbf{X}$  Dividing throughout by I<sub>dc</sub>, we get,

$$\frac{I_{ac}}{I_{dc}} = \frac{1}{I_{dc}} \sqrt{I_{rms}^2 - I_{dc}^2} \quad (But I_{ac}/I_{dc} is the ripple factor.)$$

$$\therefore \text{ Ripple factor} = \frac{1}{I_{dc}} \sqrt{I_{rms}^2 - I_{dc}^2} = \sqrt{\left(\frac{I_{rms}}{I_{dc}}\right)^2 - 1}$$

### [1.12]

#### (i) For half-wave rectification: -

:.

:.

In half-wave rectification.

rectification,

$$I_{rms} = I_m/2$$

;  $I_{dc} = I_m/\pi$

Ripple factor  $= \sqrt{\left(\frac{l_m/2}{l_m/\pi}\right)^2 - 1} = 1.21$

### 🔉 It is clear that a.c. component exceeds the d.c. component in the output of a half-wave rectifier.

$\mathbf{x}$  This results in greater pulsations in the output.

- Therefore, half-wave rectifier is ineffective for conversion of a.c. into d.c.

- For full-wave rectification -(ii)

In full-wave rectification,

$$I_{\rm rms} = \frac{I_m}{\sqrt{2}}$$

;  $I_{\rm dc} = \frac{2I_m}{\pi}$

Ripple factor  $= \sqrt{\left(\frac{I_m/\sqrt{2}}{2I_m/\pi}\right)^2 - 1} = 0.48$  i.e.  $\frac{\text{effective a.c.component}}{\text{d.c.component}} = 0.48$

- This shows that in the output of a full-wave rectifier, the d.c. component is more than the a.c. component. Consequently, the pulsations in the output will be less than in half-wave rectifier.

- > For this reason, full-wave rectification is invariably used for conversion of a.c. into d.c.

### ♣ Peak Inverse Voltage (PIV) : -

- $\sim$  The maximum value of reverse voltage occurs at the peak of the input cycle, which is equal to V<sub>m</sub>.

- 🄉 This maximum reverse voltage is called peak inverse voltage (PIV). Thus the PIV of diode :

- **a)** For Half Wave =  $V_{m_a}$ **b)** For Center Tapped =  $2V_m$  and **c)** For Bridge Rectifier =  $V_m$ .

### **Transformer Utilization Factor (TUF) : -**

A It may be defined as the ratio of d.c. power delivered to the load and the a.c. rating of the transformer secondary.

Thus,

$$TUF = P_{dc} / P_{ac}$$

▶ For half wave rectifier, TUF = 0.287; Center taped rectifier, TUF = 0.693; Bridge rectifier, TUF = 0.812.

### The TUF is very useful in determining the rating of a transformer to be used with rectifier circuit.

- **4** Average Value of Voltage & Current for HALF WAVE Rectifiers: -

- $\gtrsim$  If V<sub>m</sub> = Maximum value of the a.c. input voltage, then the average or d.c. value of the output voltage and current is given by

$$V_{dc} = V_m / \pi = 0.318 V_m$$

and  $I_{dc} = I_m / \pi = 0.318 I_m$

- **4** Average Value of Voltage & Current for FULL WAVE Rectifiers: -

- $\sim$  If V<sub>m</sub> = Maximum value of the a.c. input voltage, then the average or d.c. value of the output voltage and current is given by  $V_{dc} = 2V_m/\pi = 0.636 V_m$  and  $I_{dc} = 2I_m/\pi = 0.636 I_m$

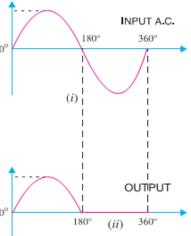

### **4** Output Frequency of Half Wave Rectifier: -

- The output frequency of a half-wave rectifier is equal to the input frequency (50 Hz). Recall how a complete cycle is defined.

- A waveform has a complete cycle when it repeats the same wave pattern over a given time.

- Thus in Fig. (i), the a.c. input voltage repeats the same wave pattern over  $0^{\circ} - 360^{\circ}$ ,  $360^{\circ} - 720^{\circ}$  and so on.

- > In Fig. (ii), the output waveform also repeats the same wave pattern over  $0^{\circ} - 360^{\circ}$ ,  $360^{\circ} - 720^{\circ}$  and so on.

- This means that when input a.c. completes one cycle, the output half wave rectified wave also completes one cycle.

- A In other words, for the half wave rectifier the output frequency is equal to the input frequency i.e.  $\mathbf{f}_{out} = \mathbf{f}_{in}$

- $\mathbf{X}$  For example, if the input frequency of sine wave applied to a half-wave  $\mathbf{x}$ rectifier is 100 Hz, then frequency of the output wave will also be 100 Hz.

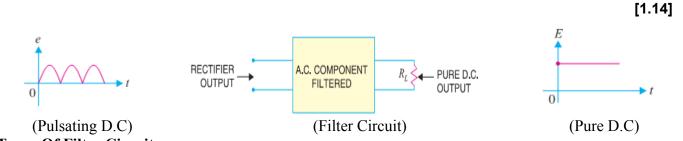

### ✤ FILTER CIRCUITS:-

- Sequence of the electronic of the electronic circuits.

- A However, the output of a rectifier has pulsating character i.e. it contains A.C. and D.C. components.

- The A.C. component is undesirable and must be kept away from the load.

- To do so, a filter circuit is used which removes (or filters out) the A.C. component and allows only the D.C. component to reach the load.

- A filter circuit is a device which removes the A.C. component of rectifier output but allows the D.C. component to reach the load.

- A filter circuit is generally a combination of inductors (L) and capacitors (C).

- ➤ A capacitor offers infinite reactance to d.c.

- So We Know that  $X_C = 1/2\pi fC$ . But for D.C., f = 0.

- :  $X_C = 1/2\pi fC = 1/2\pi x \ 0 \ x \ C = \infty$  (Means Capacitor shows *infinite reactance* to DC)

### • Hence, a Capacitor does not allow d.c. to pass through it.

- So We know  $X_L = 2\pi f L$ . For d.c., f = 0

- $\therefore$  X<sub>L</sub> = 2 $\pi$  x 0 x L = 0 (Means Inductor shows *zero reactance* to DC)

### + Hence Inductor passes d.c. quite readily.

- A Capacitor passes A.C. but does not pass D.C. at all. On the other hand, an Inductor opposes A.C. but allows D.C. to pass through it.

- A It then becomes clear that suitable network of L and C can effectively remove the A.C. component, allowing the D.C. component to reach the load.

# > Types Of Filter Circuits:-

- There are different types of filter circuits according to their construction. The most commonly used filter circuits are : -

- Inductive Filter or Series Inductor,

- \* Capacitor Filter or Shunt Capacitor,

- <u>Choke Input Filter or LC Filter</u> and

- Capacitor Input Filter or  $\pi$ -Filter.

### ✓ Inductive Filter Or Series Inductor:-

(Rectified output Pulsating d.c) (Inductive Filter Circuit)

(Output of Inductive Filter)

(Output of Capacitor Filter)

- $\gtrsim$  Fig. (ii) Shows a typical Inductive filter circuit. It consists of an Inductor L placed across the rectifier output in series with load R<sub>L</sub>.

- The choke (Inductor with iron core) offers high opposition to the passage of a.c. component but no opposition to the d.c. component.

- The result is that most of the a.c. component appears across the choke while whole of d.c. component passes through the choke on its way to load. This results in the reduced pulsations at Load resistance  $R_L$ .

- ✓ Capacitor Filter Or Shunt Capacitor:-

(Rectified output Pulsating d.c) (Capacitor Filter Circuit)

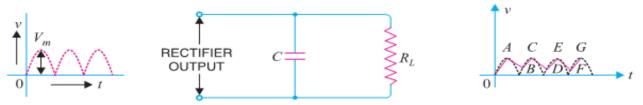

- $\thickapprox$  Fig. (ii) Shows a typical capacitor filter circuit. It consists of a capacitor C placed across the rectifier output in parallel with load R<sub>L</sub>.

- A The pulsating direct voltage of the rectifier is applied across the capacitor. As the rectifier voltage increases, it charges the capacitor and also supplies current to the load.

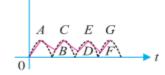

- At the end of quarter cycle [Point A in Fig. (iii)], the capacitor is charged to the peak value  $V_m$  of the rectifier voltage.

- > Now, the rectifier voltage starts to decrease. As this occurs, the capacitor discharges through the load and voltage across it decreases as shown by the line AB in Fig. (iii).

- A The voltage across load will decrease only slightly because immediately the next voltage peak comes and recharges the capacitor.

- This process is repeated again and again and the output voltage waveform becomes ABCDEFG. It may be seen that very little ripple is left in the output.

- A Moreover, output voltage is higher as it remains substantially near the peak value of rectifier output voltage.

- A The capacitor filter circuit is extremely popular because of its low cost, small size, little weight and good characteristics.

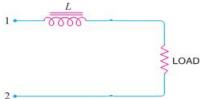

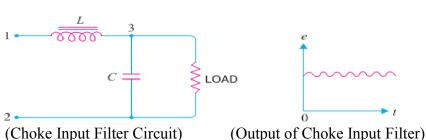

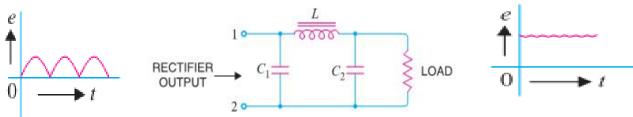

### ✓ Choke Input Filter Or LC Filter:-

(Rectified output Pulsating d.c) (Choke Input Filter Circuit)

- So Fig. shows a typical choke input filter circuit. It consists of a choke L connected in series with the rectifier output and a filter capacitor C across the load.

- A Only a single filter section is shown, but several identical sections are often used to reduce the pulsations as effectively as possible.

- The pulsating output of the rectifier is applied across terminals 1 and 2 of the filter circuit.

- As discussed before, the pulsating output of rectifier contains a.c. and d.c. components. The choke offers high opposition to the passage of a.c. component but negligible opposition to the d.c. component.

- The result is that most of the a.c. component appears across the choke while whole of d.c. component passes through the choke on its way to load. This results in the reduced pulsations at terminal 3.

- At terminal 3, the rectifier output contains d.c. component and the remaining part of a.c. component which has managed to pass through the choke.

- Now, the low reactance of filter capacitor bypasses the a.c. component but prevents the d.c. component to flow through it. Therefore, only d.c. component reaches the load.

- A In this way, the filter circuit has filtered out the a.c. component from the rectifier output, allowing d.c. component to reach the load.

- Capacitor Input Filter or π-Filter:-

(Rectified output Pulsating d.c) (Capacitor Input or  $\pi$ -Filter Circuit) (Output of  $\pi$ -Filter)

- So Fig. shows a typical capacitor input filter or  $\pi$ -filter. It consists of a filter capacitor C<sub>1</sub> connected across the rectifier output, a choke Lin series and another filter capacitor C<sub>2</sub> connected across the load.

- ➤ Only one filter section is shown but several identical sections are often used to improve the smoothing action. The pulsating output from the rectifier is applied across the input terminals (i.e. terminals 1 & 2) of the filter.

The filtering action of the three components viz C<sub>1</sub>, L and C<sub>2</sub> of this filter is described below :

(a) The filter capacitor C<sub>1</sub> offers low reactance to a.c. component of rectifier output while it offers infinite reactance to the d.c. component. Therefore, capacitor C<sub>1</sub> bypasses an appreciable amount of a.c.

component while the d.c. component continues its journey to the choke L. (b) The **choke L** offers high reactance to the a.c. component but it offers almost zero reactance to the d.c. component. Therefore, it allows the d.c. component to flow through it, while the un bypassed a.c. component is blocked.

(c) The filter capacitor  $C_2$  bypasses the a.c. component which the choke has failed to block. Therefore, only d.c. component appears across the load and that is what we desire

[1.15]

# [CHAPTER-2]

# -- [TRANSISTORS AND CIRCUIT ANALYSIS] -

### **\*** INTRODUCTION:-

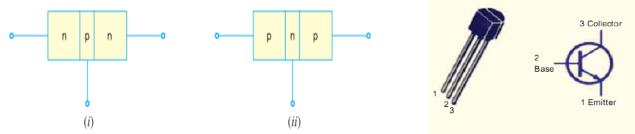

- Solution When a third doped element is added to a crystal diode in such a way that two PN junctions are formed, the resulting device is known as a **Transistor**.

- This is a new type of electronics device which can able to amplify a weak signal in a fashion comparable and often superior to that realized by vacuum tubes.

- A transistor consists of two PN junctions formed by sandwiching either p-type or n-type semiconductor between a pair of opposite types. Hence Transistor is classified into two types, namely: -

- (i) n-p-n transistor (ii) p-n-p transistor

- An n-p-n transistor is composed of two n-type semiconductors separated by a thin section of p-type.

- A However, a p-n-p transistor is formed by two p-sections separated by a thin section of n-type as shown in Figure below.

### \* NAMING: -

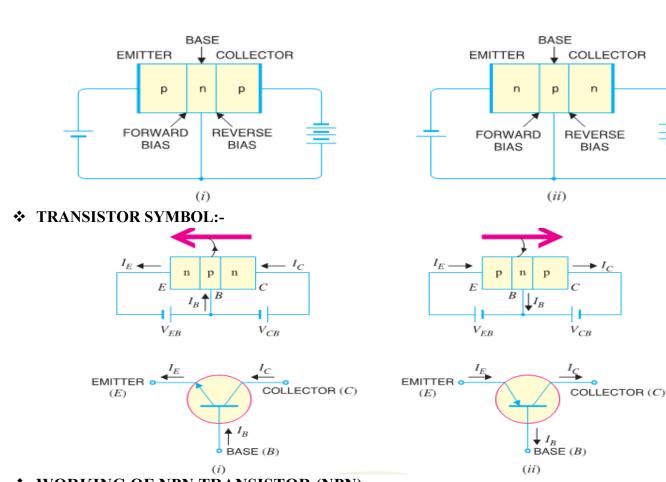

- A transistor has *two pn junctions*. As discussed later, one junction is forward biased and the other is reverse biased.

- The *forward biased junction* has a low resistance path whereas a *reverse biased junction* has a high resistance path.

- A The weak signal is introduced in the low resistance circuit and output is taken from the high resistance circuit. Therefore, a transistor transfers a signal from a low resistance to high resistance.

- A The prefix '**trans**' means the signal transfer property of the device while '**istor**' classifies it as a solid element in the same general family with resistors.

### ✤ NAMING THE TRANSISTOR TERMINALS:-

- A transistor (PNP or NPN) has three sections of doped semiconductors.

- The section on one side is the **emitter** and the section on the opposite side is the **collector**.

- The middle section is called the **base** and forms two junctions between the emitter and collector.

# 4 (i)Emitter: -

- The section on one side that *supplies charge carriers* (electrons or holes) is called the emitter.

- The emitter is always forward biased w.r.t. base so that it can supply a large number of majority carriers.

- A The emitter (p-type) of PNP transistor is forward biased and supplies hole charges to its junction with the base. Similarly the emitter (n-type) of NPN transistor has a forward bias and supplies free electrons to its junction with the base.

# 🜲 (ii) Collector: -

- The section on the other side that *collects the charges* is called the collector. The collector is always reverse biased. Its function is to remove charges from its junction with the base.

- A The collector (p-type) of PNP transistor has a reverse bias and receives hole charges that flow in the output circuit. Similarly the collector (n-type) of NPN transistor has reverse bias & receives electrons.

- 🔸 (iii)Base: -

- The middle section which forms two PN-junctions between emitter & collector is called base.

- 🆎 The base-emitter junction is forward biased, allowing low resistance for the emitter circuit.

- 🄉 The base-collector junction is reverse biased and provides high resistance in the collector circuit.

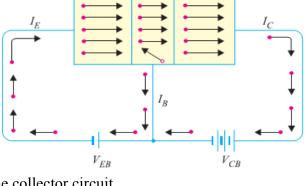

# ✤ WORKING OF NPN TRANSISTOR (NPN): -

- ➤ The NPN transistor with forward bias to emitter- base junction & reverse bias to collector-base junction.

- The forward bias causes the electrons in the n-type emitter to flow towards the base.

- This constitutes the emitter current  $I_E$ . As these electrons flow through the p-type base, they tend to combine with holes.

- As the base is lightly doped and very thin, therefore, only a few electrons (less than 5%) combine with holes to constitute base current  $I_B$ .

- The remainders (more than 95%) cross over into the collector region to constitute collector current  $I_C$ .

- 🔉 In this way, almost the entire emitter current flows in the collector circuit.

- **A** It is clear that emitter current is the sum of collector and base currents i.e.  $I_E = I_B + I_C$

### ♦ WORKING OF PNP TRANSISTOR (PNP): -

- ▶ Fig. shows the basic connection of a PNP transistor.

- The forward bias causes the holes in the p-type emitter to flow towards the base.

- $\mathbf{X}$  This constitutes the emitter current  $I_E$ .

- As these holes cross into n-type base, they tend to combine with the electrons.

- As the base is lightly doped and very thin, therefore, only a few holes (less than 5%) combine with the electrons. The remainder (more than 95%) cross into the collector region to constitute collector current  $I_C$ .

- 🔉 In this way, almost the entire emitter current flows in the collector circuit.

- A It may be noted that current conduction within PNP transistor is by holes. However, in the external connecting wires, the current is still by electrons

[2.2]

### [2.3]

### ✤ TRANSISTOR CONNECTIONS:-

- There are three leads in a transistor such as emitter, base and collector terminals.

- A However, when a transistor is to be connected in a circuit, we require **four terminals**; two for the input and two for the output.

- This difficulty is overcome by making one terminal of it in common to both input and output terminals.

- **A** The input is fed between this common terminal and one of the other two terminals.

- **The output is obtained between the common terminal and the remaining terminal.**

- >>>> So a transistor can be connected in a circuit in the following ways:-

(i) Common Base connection (ii) Common Emitter connection (iii) Common Collector connection

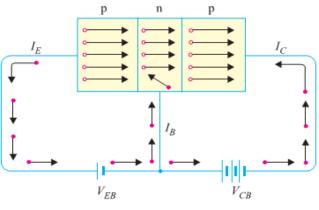

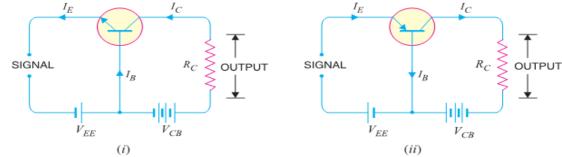

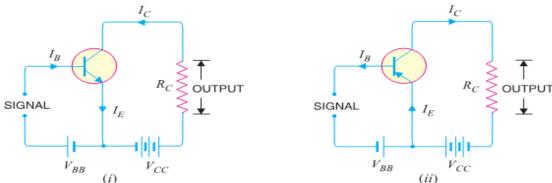

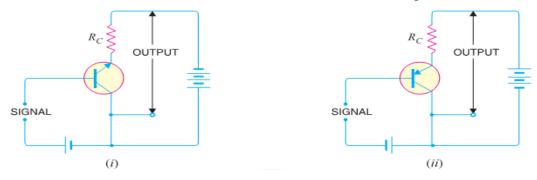

#### **4** (i)Common Base Connection

In this circuit arrangement, input is applied between emitter and base and output is taken from collector and base.

Here, base of the transistor is common to both input and output circuits and hence the name Common Base connection. A Common Base NPN and PNP in figure below.

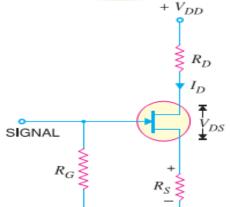

#### **4** (ii) Common Emitter Connection

In this circuit arrangement, input is applied between base and emitter and output is taken from the collector and emitter.

Here, emitter of the transistor is common to both input and output circuits and hence the name Common Emitter connection. A Common Emitter NPN and PNP transistor circuit is shown in figure below.

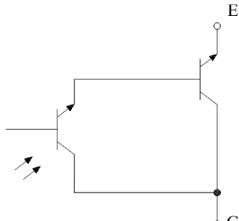

#### **4** (iii) Common Collector Connection

In this circuit arrangement, input is applied between base and collector while output is taken between the emitter and collector.

Here, collector of the transistor is common to both input and output circuits and hence the name Common Collector connection. A Common Collector NPN and PNP in figure below.

[2.4]

### \* TRANSISTOR CHARACTERISTICS:-

### **1)** Characteristics of Common Base Connection

- The complete electrical behavior of a transistor can be described by stating the interrelation of the various currents and voltages.

- These relationships can be conveniently displayed graphically and the curves thus obtained are known as the characteristics of transistor.

- The most important characteristics of common base connection are input characteristics and output characteristics.

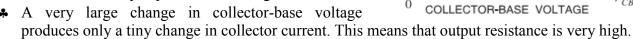

#### A) Input Characteristics:-

- $\mathbf{X}$  It is the curve between emitter current  $I_E$  & emitter-base voltage  $V_{BE}$  at constant collector-base voltage  $V_{CB}$ .

- The emitter current is generally taken along y-axis and emitter-base voltage along x-axis. Fig. Shows the input characteristics of a typical transistor in CB arrangement.

- > The following points may be noted from these characteristics :

- The emitter current  $I_E$  increases rapidly with small increase in emitter-base voltage  $V_{\text{EB}}$ . It means that input resistance is very small.

- The emitter current is almost independent of collectorbase voltage  $V_{CB}$ . This leads to the conclusion that emitter current (and hence collector current) is almost independent of collector voltage.

- **A** Input Resistance: It is the ratio of change in emitter-base voltage ( $\Delta V_{EB}$ ) to the resulting change in emitter current ( $\Delta I_E$ ) at constant collector-base voltage (V<sub>CB</sub>) i.e.

Input resistance,

$$r_i = \frac{\Delta V_{BE}}{\Delta I_E}$$

at constant  $V_{CB}$

$\sim$  In fact, input resistance is the opposition offered to the signal current. As a very small V<sub>EB</sub> is sufficient to produce a large flow of emitter current I<sub>E</sub>, thus, input resistance is quite small, of the order of a few ohms.

$I_C(mA)$

5

4

3

2

1

0

CURRENT

COLLECTOR

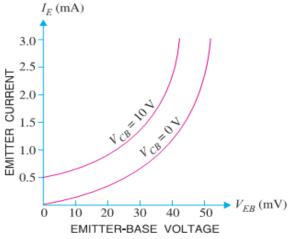

#### **B) Output Characteristics:-**

- $\gtrsim$  It is the curve between collector current I<sub>C</sub> & collector-base voltage V<sub>BC</sub> at constant emitter current I<sub>E</sub>.

- A Generally, collector current is taken along y-axis and collector-base voltage along x-axis.

- The fig. shows the input and output characteristics of a typical transistor in CB arrangement.

- $\mathbf{X}$  The following points may be noted from characteristics :

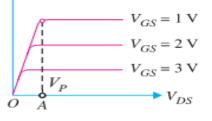

- The collector current  $I_C$  varies with  $V_{CB}$  only at very + low voltages (< 1V). The transistor is never operated in this region.

- When the value of  $V_{CB}$  is raised above 1 2 V, the \* collector current becomes constant as indicated by straight horizontal curves. It means that now I<sub>C</sub> is independent of V<sub>CB</sub> and depends upon I<sub>E</sub> only. This is consistent with the theory that the emitter current flows almost entirely to the collector terminal. The transistor is always operated in this region.

**A** Output Resistance: - It is the ratio of change in collector-base voltage ( $\Delta V_{CB}$ ) to the resulting change in collector current ( $\Delta I_C$ ) at constant emitter current i.e.

Output resistance,

$$r_o = \frac{\Delta V_{CB}}{\Delta I_C}$$

at constant  $I_E$

The output resistance of CB circuit is very high, of the order of several tens of kilo-ohms.

$I_F = 5 \text{ mA}$

$I_E = 4 \text{ mA}$

$I_F = 3 \text{ mA}$

$I_E = 2 \text{ mA}$

$I_E = 1 \text{ mA}$

$I_E = 0 \text{ mA}$

COLLECTOR-BASE VOLTAGE

V<sub>CB</sub> (VOLTS)

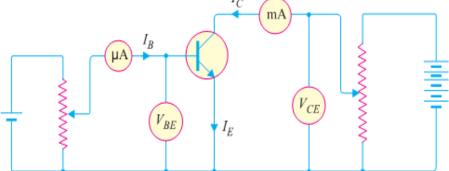

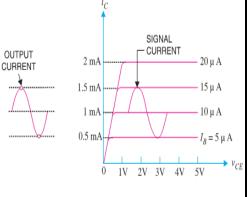

#### **4** 2) Characteristics of Common Emitter Connection:-

> The important characteristics of this circuit arrangement are the input characteristic and output characteristic.  $I_C$

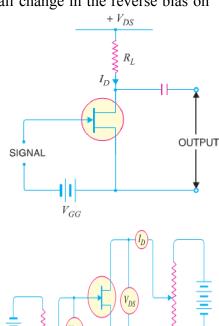

(Circuit Arrangement for studying Common Emitter Connection of Transistor)

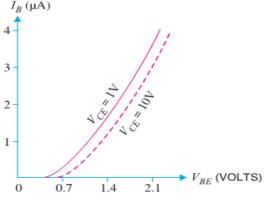

#### A) Input Characteristics:-

- It is the curve between base current IB & base-emitter voltage VBE at constant collector-emitter volt  $V_{CE}$ . The input characteristics of a CE connection can be determined by the circuit shown in Fig. Keeping  $V_{CE}$  constant

- (Let 10 V), note the base current I<sub>B</sub> for various values of V<sub>BE.</sub>

➤ Then plot the readings obtained on the graph, taking I<sub>B</sub> along y-axis and V<sub>BE</sub> along x-axis. This gives the input characteristic at V<sub>CE</sub> = 10V as shown in Fig.

> The following points may be noted from the characteristics :

The characteristic resembles that of a forward biased diode curve. This is expected since the base-emitter section of transistor is a diode and it is forward biased.

- As compared to CB arrangement,  $I_B$  increases less rapidly 0 0.7 1.4 2 with  $V_{BE}$ . Therefore, input resistance of a CE circuit is higher than that of CB circuit.

- **Input Resistance:** It is the ratio of change in base-emitter voltage ( $\Delta V_{BE}$ ) to the change in base current ( $\Delta I_B$ ) at constant V<sub>CE</sub>. The value of input resistance for CE circuit is of the order of a few hundred ohms

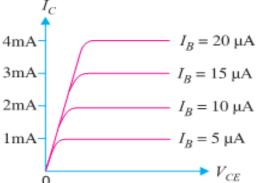

- B) Output Characteristics: -

- $\mathbf{X}$  It is the curve between collector current  $\mathbf{I}_{\mathbf{C}}$  and collector-emitter voltage  $\mathbf{V}_{\mathbf{CE}}$  at constant base current  $\mathbf{I}_{\mathbf{B}}$ .

- The output characteristics of CE circuit can be drawn with the help of above circuit arrangement in Fig.

- The Keeping the base current  $I_B$  fixed at some value say, 5  $\mu$ A, note the collector current  $I_C$  for various values of  $V_{CE}$ .

- Then plot the readings on a graph, taking  $I_C$  along y-axis and  $V_{CE}$  along x-axis.

- This gives the output characteristic at  $I_B = 5 \ \mu A$  as shown in Fig. The test can be repeated for  $I_B = 10 \ \mu A$  to obtain the new output characteristic as shown in Fig.

- Solution Following similar procedure, a family of output characteristics can be drawn as shown in Fig.

$\mathbf{x}$  The following points may be noted from the characteristics:

- (i) The collector current I<sub>C</sub> varies with V<sub>CE</sub> for V<sub>CE</sub> between 0 and 1V only. After this, I<sub>C</sub> becomes almost constant & independent of V<sub>CE</sub>. This value of V<sub>CE</sub> upto which I<sub>C</sub> changes with V<sub>CE</sub> is called the knee voltage (V<sub>knee</sub>). The transistors are always operated in the region above knee voltage.

- (ii) Above knee voltage, I<sub>C</sub> is almost constant. However, a small increase in I<sub>C</sub> with increasing V<sub>CE</sub> is caused by the collector depletion layer getting wider and capturing a few more majority carriers before electron-hole combinations occur in the base area.

• (iii) For any value of V<sub>CE</sub> above knee voltage, the collector current I<sub>C</sub> is approximately equal to  $\beta \times I_B$

**Output Resistance:** - It is the ratio of change in collector-emitter voltage ( $\Delta V_{CE}$ ) to the change in collector current ( $\Delta I_C$ ) at constant  $I_B$  i.e.  $\Delta V_{CE}$

Dutput resistance,

$$r_o = \frac{\Delta V_{CE}}{\Delta I_C}$$

at constant  $I_B$

[2.6]

- It may be noted that whereas the output characteristics of CB circuit are horizontal, they have noticeable slope for the CE circuit.

- > Therefore, output resistance of CE circuit is less than that of CB circuit. Its value is of the order of 50 k $\Omega$ .

- **4** 3) Characteristics of Common Collector Connection:-

- A In a Common Collector circuit connection the load resistor connected from emitter to ground, so the collector tied to ground even though the transistor is connected in a manner similar to the CE connection.

- A Hence there is no need for a set of common-collector characteristic to choose the parameters of the circuit. The output characteristic of the CC configuration is same as CE configuration.

- $\mathbf{x}$  For CC Connection the output characteristic are plot of  $\mathbf{I}_{\mathrm{E}}$  versus  $\mathbf{V}_{\mathrm{CE}}$  for a constant value of  $\mathbf{I}_{\mathrm{B}}$ .

- There is an almost unnoticeable change in the vertical scale of  $I_C$  of the CE connection if  $I_C$  is replaced by  $I_E$  for CC connection. The input circuit of CC connection, the CE characteristic is sufficient to obtain the required information.

# ✤ <u>CURRENT AMPLIFICATION FACTORS</u>: - (It is the ratio of output current to input current)

### 1) Common Base Connection:-

In a common base connection, the input current is the Emitter Current  $I_E$  and output current is the Collector Current  $I_C$ .

Hence the ratio of change in collector current to the change in emitter current at constant collector-base voltage V<sub>CB</sub> is known as current amplification factor for CB Connection and is denoted as  $\alpha$  (Alpha).  $\alpha = \frac{\Delta I_C}{\Delta I_E}$

• Practical values of  $\alpha$  in commercial transistors range from 0.9 to 0.99.

# 2) Common Emitter Connection:-

In a common emitter connection, the input current is the Base Current  $I_B$  and output current is the Collector Current  $I_C$ .

Hence ratio of change in collector current (I<sub>C</sub>) to the change in base current (I<sub>B</sub>) at constant collector-emitter voltage V<sub>CE</sub> is known as current amplification factor for CE Connection and denoted as  $\beta$  (Beta).

• Usually, its value ranges from 20 to 500.

# 3) Common Collector Connection:-

In a common collector connection, the input current is the Emitter Current  $I_B$  and output current is the Emitter Current  $I_E$ .

Hence the ratio of change in emitter current to the change in base current at constant  $V_{CC}$  is known as current amplification factor for CC Connection and is denoted as  $\gamma$  (Gamma).

• This circuit provides about the same current gain as the common emitter circuit as  $\Delta I_E \approx \Delta I_C$ .

**\*** RELATION AMONG DIFFERENT CURRENT AMPLIFICATION FACTORS:-  $ΔI_E = ΔI_B + ΔI_C$ 1) Relation between α and β :-

$$As, \beta = \frac{\Delta I_{C}}{\Delta I_{E}} = \frac{\Delta I_{C}}{\Delta I_{E} - \Delta I_{C}} = \frac{\Delta I_{C}/\Delta I_{E}}{1 - \Delta I_{C}/\Delta I_{E}} = \frac{\alpha}{1 - \alpha} \Rightarrow As, \alpha = \frac{\Delta I_{C}}{\Delta I_{E}} = \frac{\Delta I_{C}}{\Delta I_{E} + \Delta I_{C}} = \frac{\Delta I_{C}/\Delta I_{E}}{1 + \Delta I_{C}/\Delta I_{E}} = \frac{\beta}{1 + \beta}$$

2) Relation between  $\alpha$  and  $\gamma$  :-

• As,

$$\gamma = \frac{\Delta I_E}{\Delta I_E} = \frac{\Delta I_E}{\Delta I_E - \Delta I_C} = \frac{\Delta I_E / \Delta I_E}{1 - \Delta I_C / \Delta I_E} = \frac{1}{1 - \alpha}$$

$\Rightarrow$  As,  $\alpha = \frac{\Delta I_C}{\Delta I_E} = \frac{\Delta I_E - \Delta I_E}{\Delta I_E} = \frac{\Delta I_E / \Delta I_E - 1}{\Delta I_E / \Delta I_E} = \frac{\gamma - 1}{\gamma}$

3) Relation between  $\beta$  and  $\gamma$  :-

• As,

$$\gamma = \frac{\Delta I_E}{\Delta I_E} = \frac{\Delta I_E + \Delta I_C}{\Delta I_E} = \frac{\Delta I_B}{\Delta I_E} + \frac{\Delta I_C}{\Delta I_E} = \mathbf{1} + \beta \rightarrow As, \ \beta = \frac{\Delta I_C}{\Delta I_B} = \frac{\Delta I_E - \Delta I_B}{\Delta I_B} = \frac{\Delta I_E}{\Delta I_B} - \frac{\Delta I_E}{\Delta I_B} = \gamma - \mathbf{1}$$

4) Relation between  $\alpha$ ,  $\beta$  and  $\gamma$ :-

♣ As,

...

$$\alpha = \frac{\beta}{1+\beta} \quad \therefore \quad \beta = \frac{\alpha}{1-\alpha} \quad \therefore \quad \gamma = \frac{1}{1-\alpha} \quad \therefore \quad \gamma = 1+\beta \quad \therefore \quad \beta = \gamma+1$$

$\beta = \frac{\Delta I_C}{\Delta I_B}$

### **\*** COMPARISON OF TRANSISTOR CONNECTIONS:-

| S. No. | Characteristic    | Common base                     | Common emitter                   | Common collector            |

|--------|-------------------|---------------------------------|----------------------------------|-----------------------------|

| 1.     | Input resistance  | Low (about 100 Ω)               | Low (about 750 $\Omega$ )        | Very high (about<br>750 kΩ) |

| 2.     | Output resistance | Very high (about<br>450 kΩ)     | High (about 45 k $\Omega$ )      | Low (about 50 Ω)            |

| 3.     | Voltage gain      | about 150                       | about 500                        | less than 1                 |

| 4.     | Applications      | For high frequency applications | For audio frequency applications | For impedance matching      |

| 5.     | Current gain      | No (less than 1)                | High (β)                         | Appreciable                 |

- Out of the three transistor connections, the **Common Emitter Circuit** is the most efficient.

- It is used in about 90 to 95 per cent of all transistor applications.

- The main reasons for the widespread use of this circuit arrangement are :

(i) High current gain. (ii) High voltage and power gain. (iii) Moderate output to input impedance ratio.

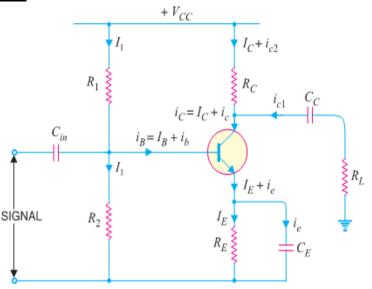

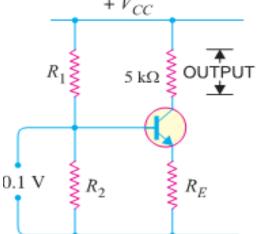

# \* D.C. AND A.C. EQUIVALENT CIRCUITS: -

- X Various circuit currents. It is useful to mention the various currents in the complete amplifier circuit. These are shown in the circuit of Fig.

- ★ (i) Base Current: When no signal is applied in the base circuit, D.C. base current I<sub>B</sub> flows due to biasing circuit. When A.C. signal is applied, A.C. base current i<sub>b</sub> also flows.

- Therefore, with the application of signal, Total Base Current  $i_B$  is given by:  $i_B = I_B + i_b$

- (ii) Collector Current: When no signal is applied, a D.C. collector current I<sub>C</sub> flows due to biasing circuit. When A.C. signal is applied, A.C. collector current i<sub>c</sub> also flows.

- **A** Therefore, the Total Collector Current  $i_C$  is given by:  $i_C = I_C + i_c$

Where  $I_C = \beta I_B =$  zero signal collector current and  $i_c = \beta i_b =$  collector current due to signal.

- **(iii) Emitter Current:-** When no signal is applied, a D.C. emitter current  $I_E$  flows. When A.C. signal is applied, A.C. Emitter Current  $i_e$  also flows. Therefore the Total Emitter Current is :  $i_E = I_E + i_e$

- **X** It is useful to keep in mind that:  $I_E = I_B + I_C$  and  $i_e = i_b + i_c$ .

**B** But base current is usually very small, therefore, as a reasonable approximation,  $I_E \approx I_C$  and  $i_e \approx i_c$ .

- D. C. Equivalent Circuit: In order to draw the equivalent D.C. circuit, the following two steps are applied to the transistor circuit: (a) Reduce all A.C. sources to zero.

- (b) Open all the capacitors.

- Referring D.C. Equivalent Circuit

D.C. Load

$$R_{DC} = R_C + R_E$$

&  $V_{CC} = V_{CE} + I_C (R_C + R_E)$

▶ The maximum value of  $V_{CE}$  will occur when there is no collector current i.e.  $I_C=0$ .

- Maximum V<sub>CE</sub>= V<sub>CC</sub>

- > The maximum collector current will flow when  $V_{CE}=0$ .

Maximum  $I_C = V_{CC} / (R_C + R_E)$

:.

...

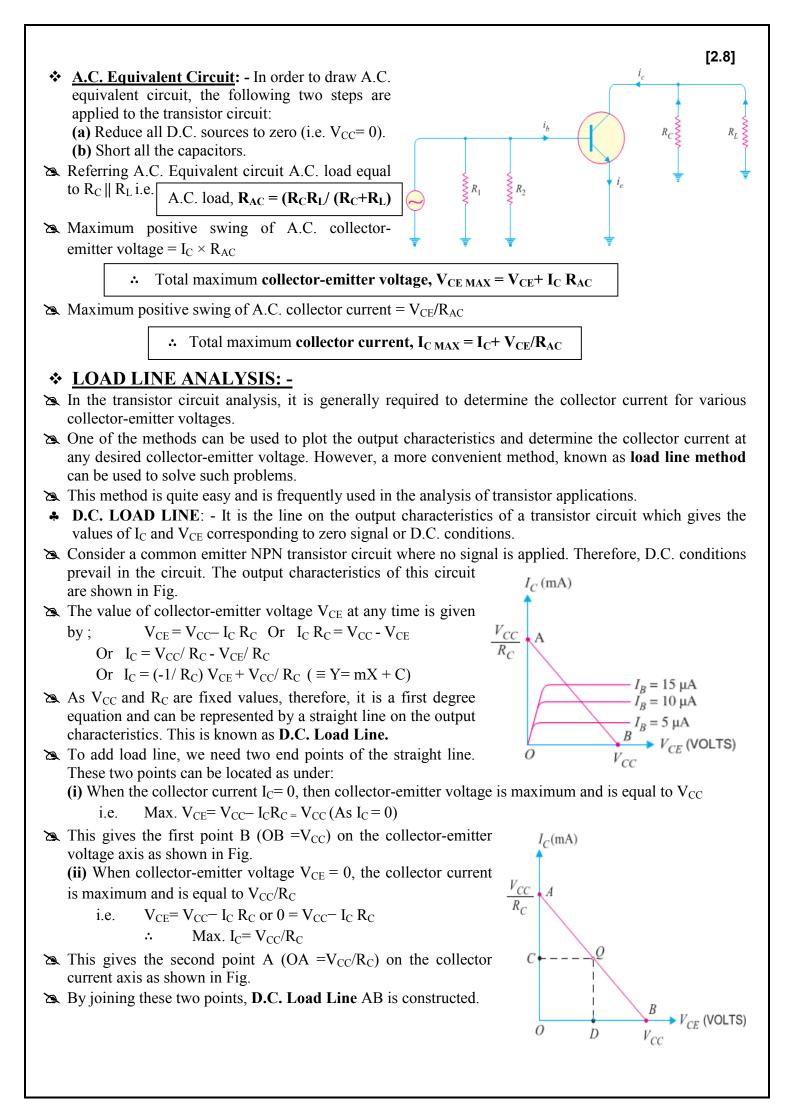

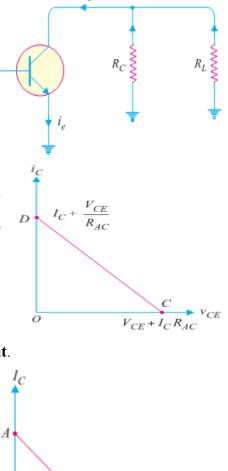

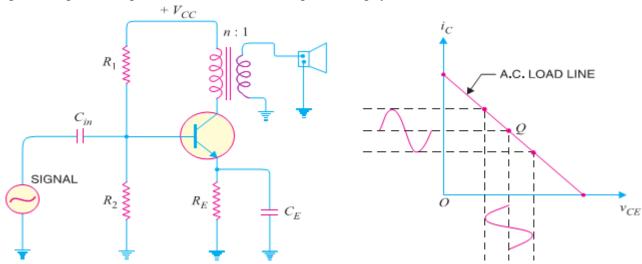

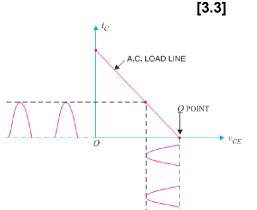

- (II) A.C. LOAD LINE. This is the line on the output characteristics of a transistor circuit which gives the values of  $i_C$  and  $v_{CE}$  when signal is applied.

- Referring back to the transistor amplifier shown in Fig., its A.C. equivalent circuit as far as output circuit is concerned is as shown in Fig.

- ➤ To add A.C. load line to the output characteristics, we again require two end points: -

- 1. One maximum collector-emitter voltage point ( $V_{CE MAX}$ ) and 2. Other is maximum collector current point. ( $I_{C MAX}$ )

- $\mathbf{X}$  Under the application of A.C. signal, these values are Maximum collector-emitter voltage,  $\mathbf{V}_{CE MAX} = \mathbf{V}_{CE} + \mathbf{I}_C \mathbf{R}_{AC}$ .

- This locates the point C of the A.C. load line on the collector-emitter voltage axis.

- $\therefore$  Maximum collector current,  $I_{C MAX} = I_C + V_{CE}/R_{AC}$

- This locates the point D of A.C. load line on the collector-current axis.

- A By joining points C and D, the A.C. Load Line CD is constructed.

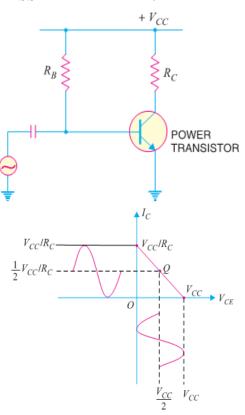

### **♦** <u>OPERATING POINT: -</u>

- **The zero signal values of**  $I_C$  and  $V_{CE}$  are known as the **Operating point**.

- The second seco

- **A** It is also called quiescent (silent) point or **Q-Point** because it is the point on  $I_C V_{CE}$  characteristic when the transistor is silent i.e. in the absence of the signal.

- Suppose in the absence of signal, the base current is  $5\mu A$ . Then  $I_C$  and  $V_{CE}$  conditions in the circuit must be represented by some point on  $I_B = 5 \ \mu A$  characteristic.

- **B** But  $I_C$  and  $V_{CE}$  conditions in the circuit should also be represented by some point on the d. c. load line AB.

- The point Q where the load line and the characteristic intersect is O C B C B C C B the only point which satisfies both these conditions. Therefore, the point Q describes the actual state of affairs in the circuit in the zero signal conditions and is called the operating point. Referring to Fig, for I<sub>B</sub>  $= 5 \mu$ A, the zero signal values are :

$$V_{CE} = OC \text{ volts}$$

$I_C = OD mA$

$\sim$  It follows, therefore, that the zero signal values of I<sub>C</sub> and V<sub>CE</sub> (i.e. operating point) are determined by the point where d.c. load line intersects at proper base current curve.

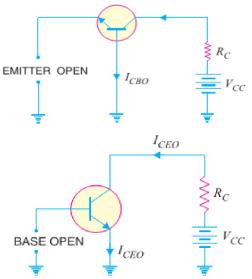

### ★ <u>THE LEAKAGE CURRENT</u>:-

- A The current is due to the movement of minority carriers is known as Leakage Current.

- **A** In Common Base Connection of Transistor the leakage current  $I_{CBO}$  is the Collector-Base current with emitter open.

- Similarly, In Common Emitter Connection the leakage current  $I_{CEO}$  is the Collector-Emitter Current with open Base.

- Expression for collector current in Common Base Connection is given by,  $I_{C} = \frac{\alpha}{I_{CBO}} I_{CBO}$

$$I_C = \frac{\alpha}{1-\alpha}I_B + \frac{I_{CBO}}{1-\alpha}$$

Expression for collector current in Common Emitter Connection is given by,

$$I_C = \frac{\alpha}{1-\alpha}I_B + \frac{1}{1-\alpha}I_{CBO} \quad \text{Or} \quad I_C = \frac{\alpha}{1-\alpha}I_B + I_{CEO}$$

$I_R = 5 \mu A$

i<sub>h</sub>

[2.9]

# **♦** FAITHFUL AMPLIFICATION :-

- The process of raising the strength of a weak signal without any change in its general shape is known as *Faithful Amplification*. The key factor for achieving faithful amplification: -

- (i) Proper zero signal collector current

- $\clubsuit$  (ii) Minimum proper base-emitter voltage (V\_{BE}) at any instant

- $\clubsuit$  (iii) Minimum proper collector-emitter voltage (V\_{CE}) at any instant

# **\*** TRANSISTOR BIASING: -

- A The proper flow of zero signal collector current and the maintenance of proper collector-emitter voltage during the passage of signal is known as *Transistor Biasing*.

- ▶ The following are the most commonly used methods of obtaining transistor biasing from one source of supply (i.e. V<sub>CC</sub>):

- ♣ (i) Base Resistor Method

- ♣ (ii) Emitter Bias Method

- ♣ (iii) Biasing with Collector-Feedback Resistor

- (iv) Voltage-Divider Bias.

# **\*** STABILISATION: -

- The process of making operating point independent of temperature changes or variations in transistor parameters is known as *Stabilization*.

- NEED FOR STABILIZATION:- Stabilization of the operating point is necessary due to the following reasons :

- (i) Temperature dependence of IC

- (ii) Individual variations

- (iii) Thermal runaway

# **\* STABILITY FACTOR :-**

Or

The rate of change of collector current  $I_C$  w.r.t. the collector leakage current  $I_{CO}$  [ =  $I_{CEO}$ ] at constant  $\beta$ and  $I_B$  is called stability Stability factor,  $S = \frac{dI_C}{dI_{CO}}$  at constant  $I_B$  and  $\beta$  factor i.e.

# ✤ <u>SIMPLE PROBLEMS ON TRANSISTOR: -</u>

1. In a common base connection,  $I_E = 1$ mA,  $I_C = 0.95$ mA. Calculate the value of  $I_B$ .

**Solution:** Using the relation,  $I_E = I_B + I_C$

$$1 = I_{\rm B} + 0.95$$

$\therefore$   $I_{\rm B} = 1 - 0.95 = 0.05 \text{ mA}$

2. In a common base connection, current amplification factor is 0.9. If the emitter current is 1mA, determine the value of base current.

Solution:Here,

$$\alpha = 0.9$$

, $I_E = 1 \text{ mA}$ Now $\alpha = \frac{I_C}{I_E}$ Or $I_C = \alpha I_E = 0.9 \times 1 = 0.9 \text{ mA}$ Also $I_E = I_B + I_C$  $\therefore$ Base current,  $I_B = I_E - I_C = 1 - 0.9 = 0.1 \text{ mA}$

3. In a common base connection, the emitter current is 1mA. If the emitter circuit is open, the collector current is 50  $\mu$ A. Find the total collector current. Given that  $\alpha$ = 0.92.

**Solution:** Here,  $I_E = 1 \text{ mA}$ ,  $\alpha = 0.92$ ,  $I_{CBO} = 50 \text{ }\mu\text{A}$

: Total collector current,  $I_C = \alpha I_E + I_{CBO} = 0.92 \times 1 + 50 \times 10^{-3} = 0.92 + 0.05 = 0.97 \text{ mA}$

4. In a common base connection,  $\alpha = 0.95$ . The voltage drop across 2 k $\Omega$  resistance which is connected in the collector is 2V. Find the base current.

| Solution: | The voltage drop across $R_C (= 2 \text{ k}\Omega)$ is 2V. |                      | <b></b> | $I_C = 2 V/2 k\Omega = 1 mA$                                              |

|-----------|------------------------------------------------------------|----------------------|---------|---------------------------------------------------------------------------|

|           | Now                                                        | $\alpha = I_C / I_E$ |         | $I_{\rm E} = \frac{I_{\rm C}}{\alpha} = \frac{1}{0.95} = 1.05 \text{ mA}$ |

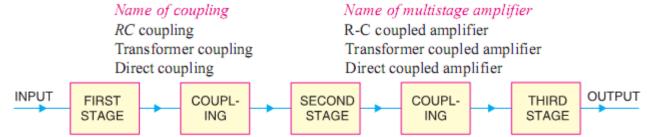

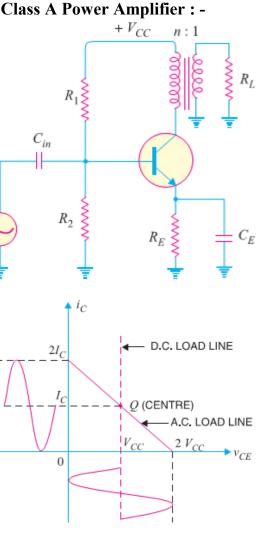

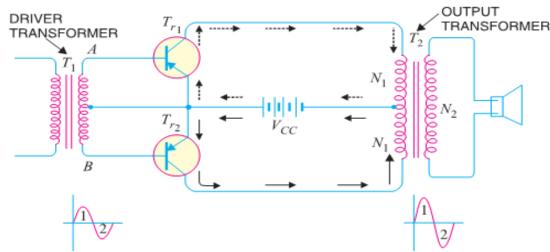

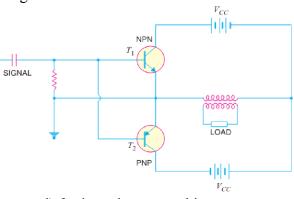

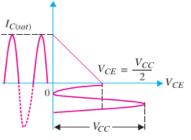

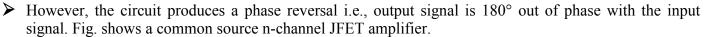

|           | Using the relation, $I_E$                                  | $= I_B + I_C$        |         | $I_B = I_E - I_C = 1.05 - 1 = 0.05 \text{ mA}$                            |